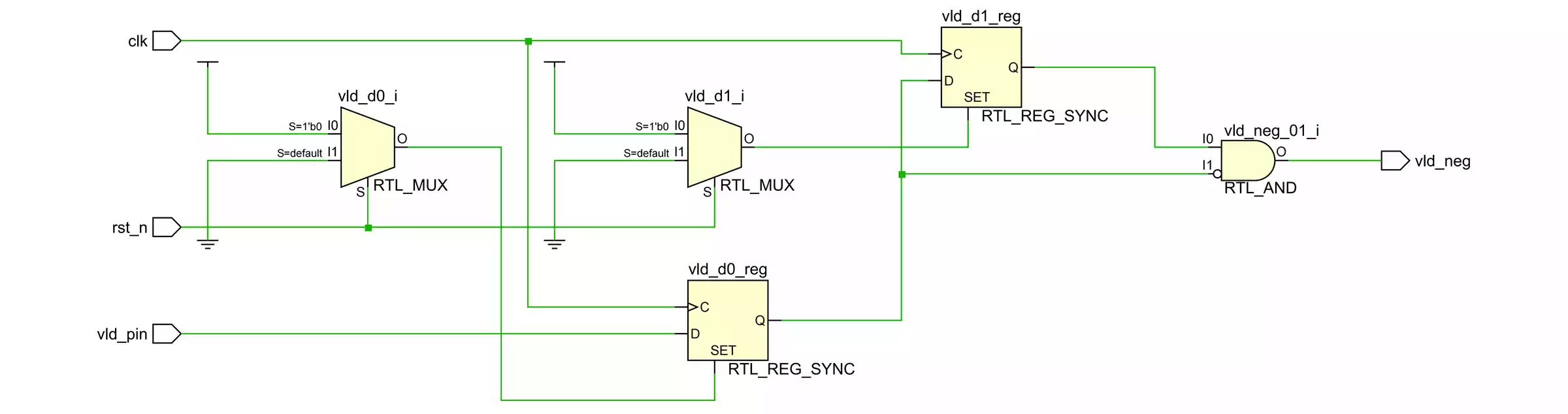

信号边沿检测

| 名称 | I/O | 说明 |

|---|---|---|

clk |

I | 时钟信号 |

rst_n |

I | (同步)复位 |

edge_pin |

I | 待检测信号 |

edge_neg |

O | 边沿 |

测试程序中的 edge_pin

为待检测边沿的信号,edge_d0 和 edge_d1

分别为延迟信号。

1 | always@(posedge clk) begin |

为了检测 edge_pin

的边沿,我暂时可以想到以下几种方法(经测试后仅部分可行)

- 时序逻辑

1 | always @(posedge clk ) begin |

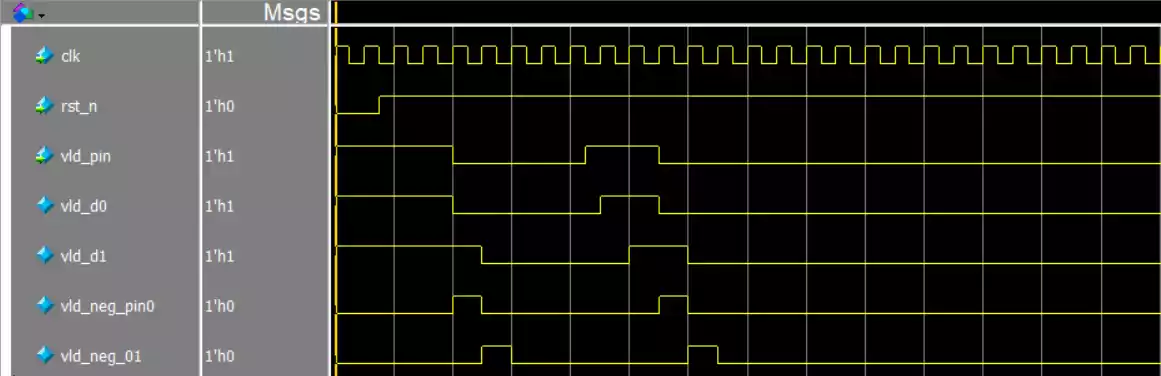

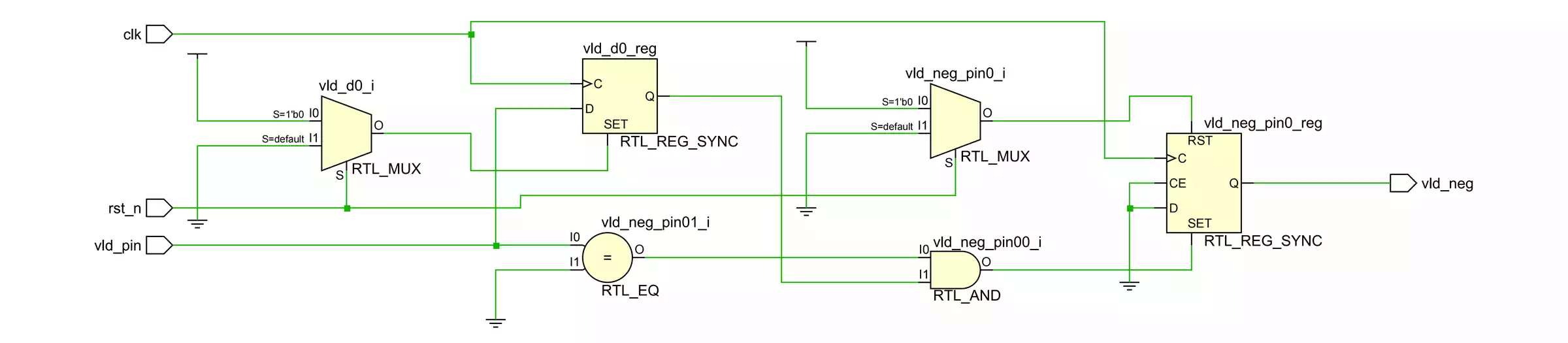

仿真结果如下图所示

由仿真结果可知,neg_pin0 能够检测到 pin

信号的下降沿,而 neg_01

虽然能够检测到下降沿,但是会延迟一个时钟周期。

- 组合逻辑

1 | assign edge_neg_pin0 = edge_pin && ~edge_d0; |

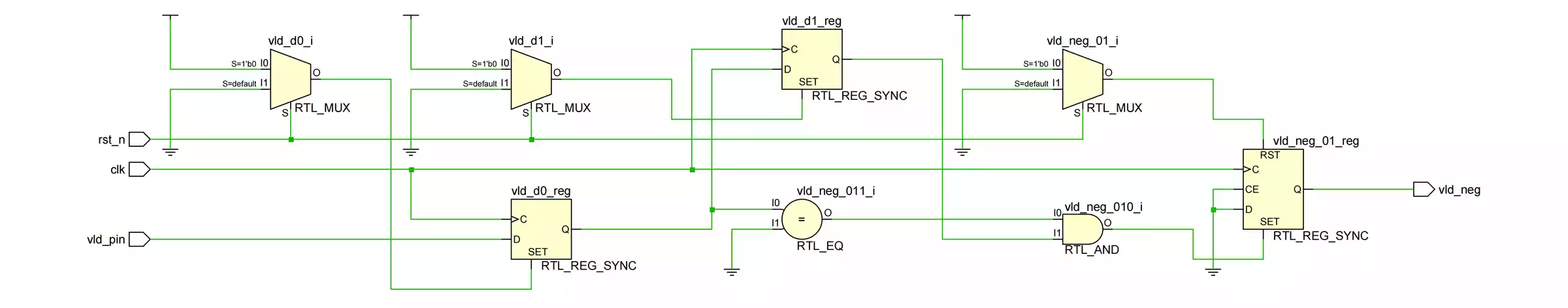

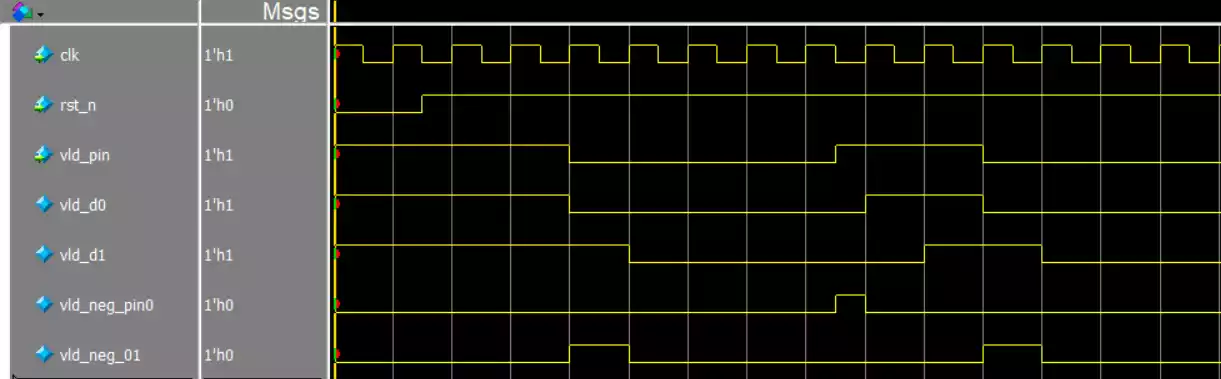

仿真结果如图所示

由仿真结果可知,neg_pin0

不能检测到下降沿,neg_01 可以检测到下降沿。

第二次

pin信号变化不在时钟上升沿,所以d0信号不会立刻随之变化,使得pin0信号检测到pin信号的上升沿;但是pin和d0都会在下个时钟上升沿变为低电平,所以不能通过 edge_pin && ~edge_d0检测到pin下降沿。

边沿的检测不应该受到时钟边沿变化的影响: 上面代码中

edge_d0 和 edge_d1

的赋值逻辑确保了在时钟周期的任何时刻,edge_d1 和

edge_d0 都有稳定的值,因此它们的异或结果

edge_neg_01 也是稳定的,不会因为时钟边沿的变化而改变。

edge_pin && ~edge_d0:edge_pin变化时刻未知:时钟上升沿变化,两者时钟相同,永远检测不到下降沿;其它时刻变化,暂时没在仿真中发现问题;edge_pin && ~edge_d1:得到edge_d1前提是有edge_d0延迟一个时钟周期,而且edge_d0比edge_pin更稳定;

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 科海拾零!

评论