时序分析

时序约束

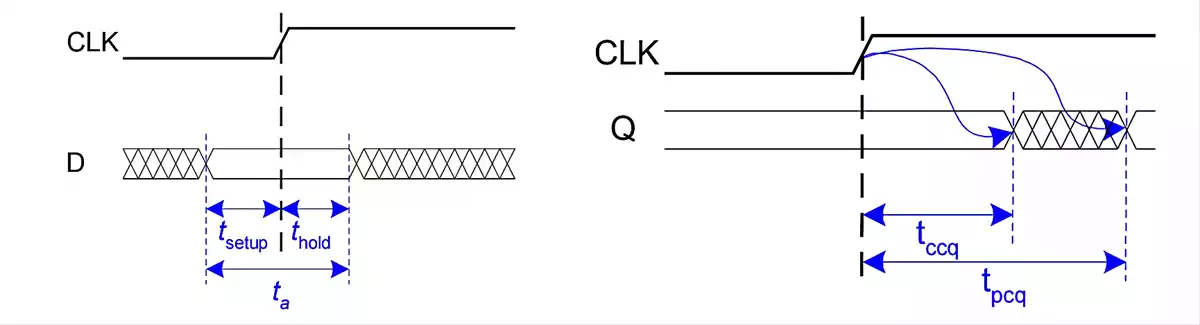

建立时间

:在时钟上升沿的 时间前数据必须是稳定的; 保持时间

:时钟上升沿之后的 时间内数据必须是稳定的; 传播延迟

:时钟上升沿到输出端信号稳定所需要的时间; 污染延迟

:时钟上升沿到输出端信号开始变化所需要的时间;

建立时间与保持时间

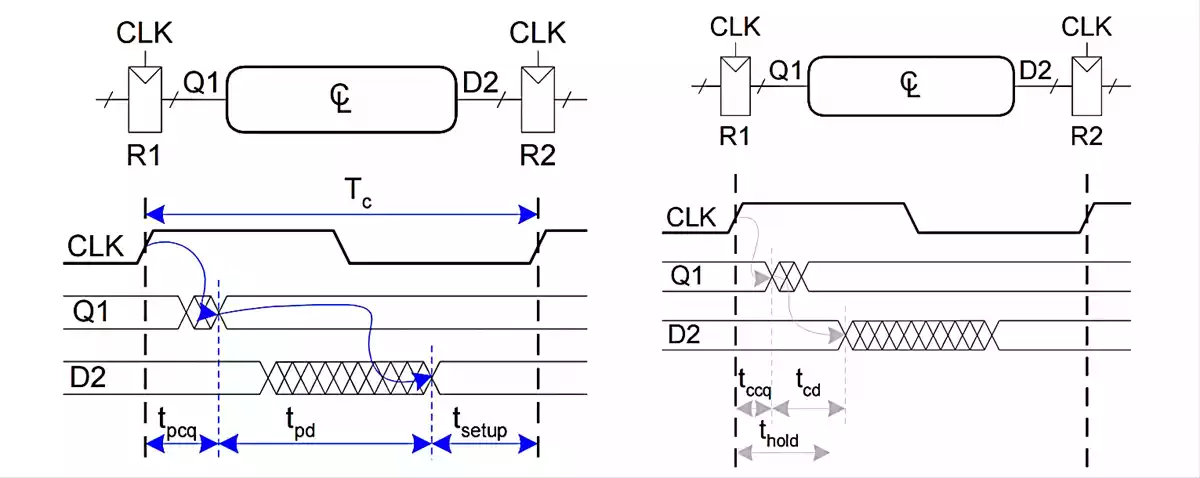

如左图所示,对

如右图所示,在

时钟偏移与抖动

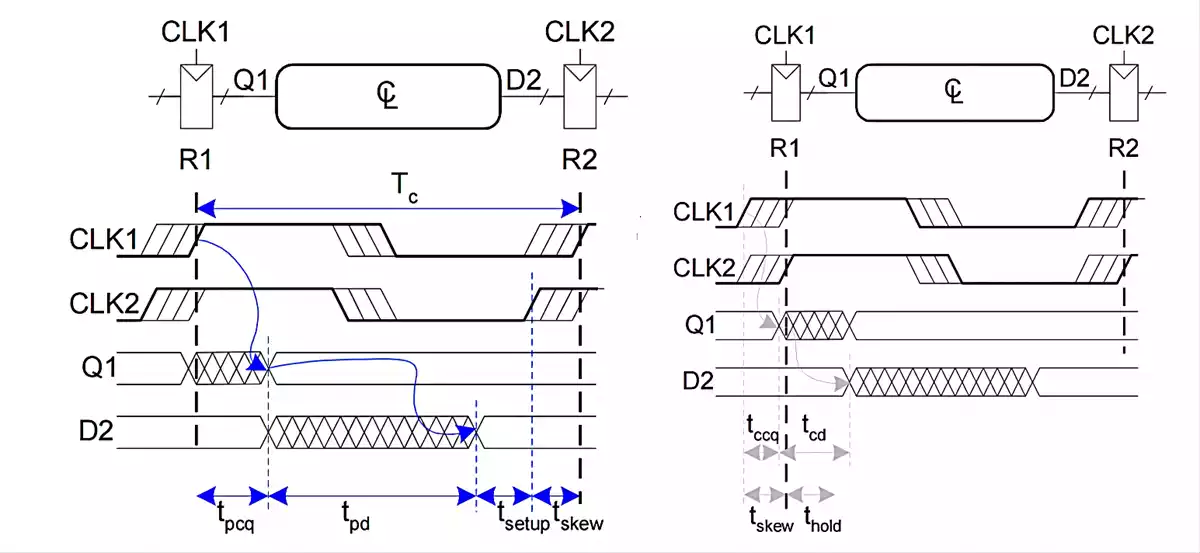

时钟偏移(Clock Skew)

时钟信号到达各寄存器的时间不同,将

如左图,由于 CLK2 比 CLK1 早了

如右图,CLK2 比 CLK1 晚了

注:相反的时钟信号关系不会影响上述的时序约束。

时钟抖动(Clock Jitter)

Skew 会改变时钟边沿的顺序,不会改变时钟信号的占空比;时钟抖动会改变时钟信号的占空比。

考虑时钟抖动时,要考虑 “最差的情况”。分析过程与 时钟偏移(Clock Skew) 相似。

参考资料

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 科海拾零!

评论