锁相环

时钟生成

晶振可以产生稳定的时钟周期,但频率只能是在兆赫兹的量级。PLL 利用晶振作为参考时钟,可以输出一个更高频率的时钟信号,提供给时序电路使用。

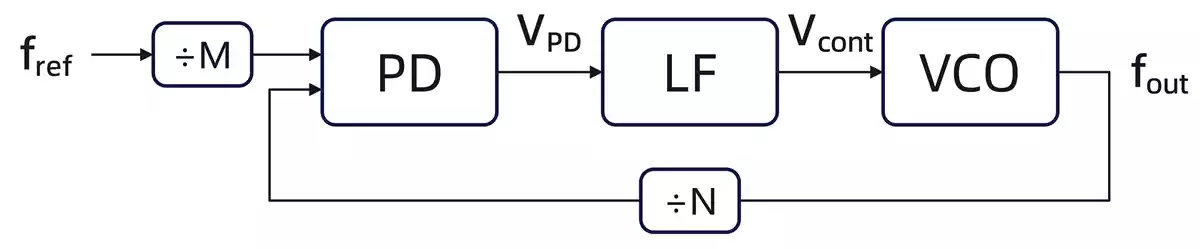

如图所示,锁相环(Phase-Locked

Loop,PLL)由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成。实现的是输出

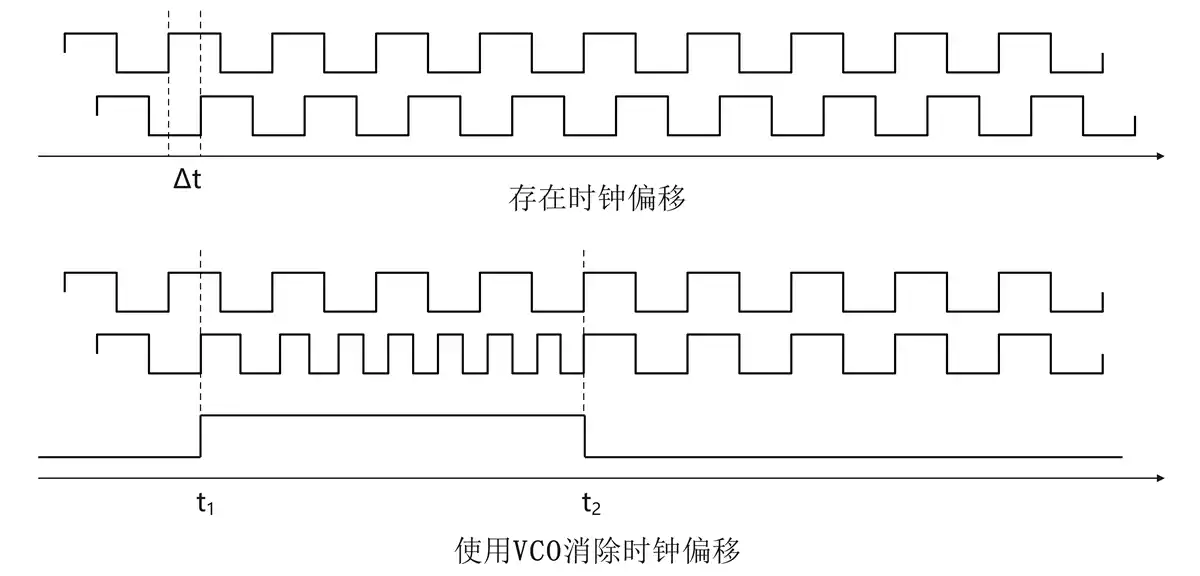

PLL 的原理是其中的 VCO 的振荡频率随着输入电压变化而变化,它的输出就是整个 PLL 的输出,也就是我们最终拿到的时钟信号。VCO 的输出会反馈回 PLL,由 PD 比较他们两 者的相位。如果晶振相位稍快,就把 VCO 输入电压调低,如果晶振相位稍慢,就把 VCO 输入电压调高,从而得到稳定的高频时钟信号。

数据重定时

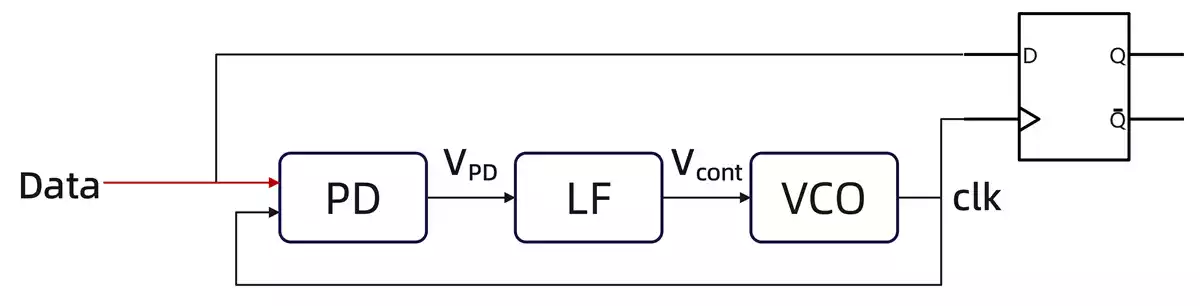

PLL 还可以用来做时钟恢复和数据重定时。

如图所示,经过传输线后的信号波形变得不稳定。可以考虑将数据作为参考,输入到 PLL 中,恢复 一个与数据同步的时钟,用该时钟信号和 D 触发器重新对数据采样,得到新的 重定时数据。

参考资料

- 张肃文.高频电子线路.第 5 版 [M].高等教育出版社,2009.432-458

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 科海拾零!

评论